Produits Catégorie

- Transmetteur FM

- 0-50w 50w-1000w 2kw-10kw 10kw +

- TV Transmetteur

- 0-50w 50-1kw 2kw-10kw

- Antenne FM

- Antenne TV

- Antenne accessoire

- Câble connecteur diviseur de puissance charge dummy

- RF Transistor

- Alimentation

- Équipements audio

- DTV avant Équipement Fin

- System Link

- système STL système de liaison à micro-ondes

- Radio FM

- Wattmètre

- Nos autres produits

- Spécial pour Coronavirus

Produits Mots

Sites Fmuser

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net -> Afrikaans

- sq.fmuser.net -> albanais

- ar.fmuser.net -> arabe

- hy.fmuser.net -> Armenian

- az.fmuser.net -> azerbaïdjanais

- eu.fmuser.net -> basque

- be.fmuser.net -> biélorusse

- bg.fmuser.net -> Bulgare

- ca.fmuser.net -> catalan

- zh-CN.fmuser.net -> chinois (simplifié)

- zh-TW.fmuser.net -> Chinois (traditionnel)

- hr.fmuser.net -> croate

- cs.fmuser.net -> tchèque

- da.fmuser.net -> danois

- nl.fmuser.net -> Néerlandais

- et.fmuser.net -> estonien

- tl.fmuser.net -> Philippin

- fi.fmuser.net -> finnois

- fr.fmuser.net -> Français

- gl.fmuser.net -> Galicien

- ka.fmuser.net -> géorgien

- de.fmuser.net -> allemand

- el.fmuser.net -> Grec

- ht.fmuser.net -> Créole haïtien

- iw.fmuser.net -> hébreu

- hi.fmuser.net -> Hindi

- hu.fmuser.net -> Hongrois

- is.fmuser.net -> islandais

- id.fmuser.net -> indonésien

- ga.fmuser.net -> irlandais

- it.fmuser.net -> Italien

- ja.fmuser.net -> japonais

- ko.fmuser.net -> coréen

- lv.fmuser.net -> letton

- lt.fmuser.net -> Lituanien

- mk.fmuser.net -> macédonien

- ms.fmuser.net -> malais

- mt.fmuser.net -> maltais

- no.fmuser.net -> Norwegian

- fa.fmuser.net -> persan

- pl.fmuser.net -> polonais

- pt.fmuser.net -> portugais

- ro.fmuser.net -> Roumain

- ru.fmuser.net -> russe

- sr.fmuser.net -> serbe

- sk.fmuser.net -> slovaque

- sl.fmuser.net -> Slovène

- es.fmuser.net -> espagnol

- sw.fmuser.net -> Swahili

- sv.fmuser.net -> suédois

- th.fmuser.net -> Thai

- tr.fmuser.net -> turc

- uk.fmuser.net -> ukrainien

- ur.fmuser.net -> ourdou

- vi.fmuser.net -> Vietnamienne

- cy.fmuser.net -> Gallois

- yi.fmuser.net -> Yiddish

Qu'est-ce que Half Adder : schéma de circuit et ses applications

Date:2021/10/18 21:55:58 Hits:

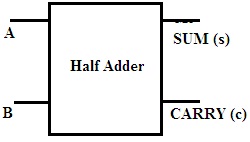

Half Adder est du type de circuit numérique de base. Auparavant, diverses opérations étaient effectuées dans les circuits analogiques. Après la découverte de l'électronique numérique, des opérations similaires y sont effectuées. Les systèmes numériques sont considérés comme efficaces et fiables. Parmi les différentes opérations, l'une des opérations les plus importantes est l'arithmétique. Il comprend l'addition, la soustraction, la multiplication et la division. Cependant, on sait déjà qu'il pourrait s'agir d'un ordinateur, n'importe quel gadget électronique comme une calculatrice peut effectuer des opérations mathématiques. Ces opérations sont effectuées sont constituées de valeurs binaires. Ceci est possible par la présence de certains circuits en elle. Ces circuits sont appelés additionneurs et soustracteurs binaires. Ce type de circuits est conçu pour les codes binaires, les codes Excess-3 et d'autres codes également. D'autres additionneurs binaires sont classés en deux types. Ils sont : Half Adder andFull AdderQu'est-ce qu'un Half Adder ? Un circuit électronique numérique qui fonctionne pour effectuer l'addition sur les nombres binaires est défini comme Half Adder. Le processus d'addition est dénié, la seule différence est le système de nombre choisi. Il n'existe que 0 et 1 dans la numération binaire. Le poids du nombre est entièrement basé sur les positions des chiffres binaires. Parmi ceux 1 et 0, 1 est traité comme le plus grand chiffre et 0 comme le plus petit. Le schéma fonctionnel de cet additionneur est Half AdderHalf Adder Circuit DiagramUn demi-additionneur se compose de deux entrées et produit deux sorties. Il est considéré comme le plus simple des circuits numériques. Les entrées de ce circuit sont les bits sur lesquels l'addition doit être effectuée. Les sorties obtenues sont la somme et le report.

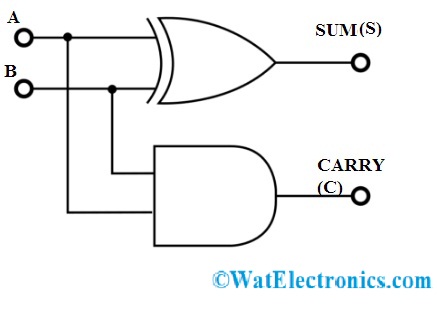

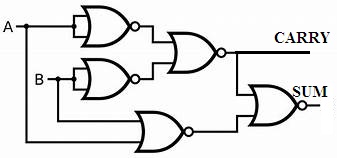

Half AdderHalf Adder Circuit DiagramUn demi-additionneur se compose de deux entrées et produit deux sorties. Il est considéré comme le plus simple des circuits numériques. Les entrées de ce circuit sont les bits sur lesquels l'addition doit être effectuée. Les sorties obtenues sont la somme et le report.  Demi-additionneurLe circuit de cet additionneur comprend deux portes. Ce sont des portes ET et XOR. Les entrées appliquées sont les mêmes pour les deux portes présentes dans le circuit. Mais la sortie est prise de chaque porte. La sortie de la porte XOR est appelée SUM et la sortie de AND est connue sous le nom de CARRY. Half Adder Truth TablePour obtenir la relation entre la sortie obtenue et l'entrée appliquée, vous pouvez analyser à l'aide d'une table appelée table de vérité.

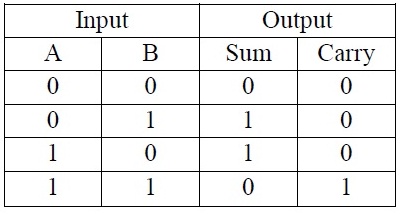

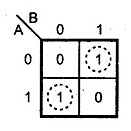

Demi-additionneurLe circuit de cet additionneur comprend deux portes. Ce sont des portes ET et XOR. Les entrées appliquées sont les mêmes pour les deux portes présentes dans le circuit. Mais la sortie est prise de chaque porte. La sortie de la porte XOR est appelée SUM et la sortie de AND est connue sous le nom de CARRY. Half Adder Truth TablePour obtenir la relation entre la sortie obtenue et l'entrée appliquée, vous pouvez analyser à l'aide d'une table appelée table de vérité. Table de vérité de demi-additionneur D'après la table de vérité ci-dessus, les points sont évidents comme suit : Si A=0, B=0 c'est-à-dire que les deux entrées appliquées sont 0. Alors les deux sorties SUM et CARRY sont 0.Parmi deux entrées appliquées si quelqu'un le l'entrée est 1, alors la SOMME sera e1 mais le CARRY est 0. Si les deux entrées sont 1, alors la SUM sera égale à 0 et le CARRY sera égal à 1. Sur la base des entrées appliquées, le demi-additionneur procède à l'opération d'addition.Équation L'équation pour ce type de circuits peut être réalisée par les concepts de Somme de Produits (SOP) et de Produits de Somme (POS). L'équation booléenne pour ce type de circuits détermine la relation entre les entrées appliquées aux sorties obtenues. Pour déterminer l'équation, les k-maps sont dessinées sur la base des valeurs de la table de vérité. Il se compose de deux équations car deux portes logiques y sont utilisées. La k-map du report est

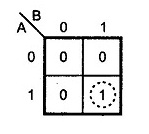

Table de vérité de demi-additionneur D'après la table de vérité ci-dessus, les points sont évidents comme suit : Si A=0, B=0 c'est-à-dire que les deux entrées appliquées sont 0. Alors les deux sorties SUM et CARRY sont 0.Parmi deux entrées appliquées si quelqu'un le l'entrée est 1, alors la SOMME sera e1 mais le CARRY est 0. Si les deux entrées sont 1, alors la SUM sera égale à 0 et le CARRY sera égal à 1. Sur la base des entrées appliquées, le demi-additionneur procède à l'opération d'addition.Équation L'équation pour ce type de circuits peut être réalisée par les concepts de Somme de Produits (SOP) et de Produits de Somme (POS). L'équation booléenne pour ce type de circuits détermine la relation entre les entrées appliquées aux sorties obtenues. Pour déterminer l'équation, les k-maps sont dessinées sur la base des valeurs de la table de vérité. Il se compose de deux équations car deux portes logiques y sont utilisées. La k-map du report est  K-Map AND GateL'équation de sortie de CARRY est obtenue à partir de la porte AND.C=A.BL'expression booléenne pour la SOMME est réalisée par la forme SOP. Par conséquent, la K-map pour la SOMME est

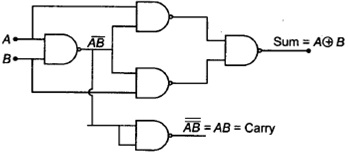

K-Map AND GateL'équation de sortie de CARRY est obtenue à partir de la porte AND.C=A.BL'expression booléenne pour la SOMME est réalisée par la forme SOP. Par conséquent, la K-map pour la SOMME est K-Map for Sum (XOR) L'équation déterminée estS= A⊕ BApplicationsLes applications de cet additionneur de base sont les suivantesPour effectuer des additions sur des bits binaires, l'unité arithmétique et logique présente dans l'ordinateur préfère ce circuit additionneur. à la formation du circuit Full Adder. Ces circuits logiques sont préférés dans la conception des calculatrices. Pour calculer les adresses et les tables, ces circuits sont préférés. Au lieu d'une simple addition, ces circuits sont capables de gérer diverses applications dans les circuits numériques. De plus, cela devient le cœur de l'électronique numérique.Code VHDLLe code VHDL pour le circuit Half Adder islibrary ieee;utiliser ieee.std_logic_1164.all;entity half_adder isport(a,b: in bit; sum, carry:out bit);end half_adder ;données d'architecture de half_adder isbeginsum<= a xor b;carry <= a et b;end data;FAQs1. Qu'entendez-vous par Adder ? Les circuits numériques dont le seul but est d'effectuer l'addition sont appelés Adders. Ce sont les principaux composants des ALU. Les additionneurs fonctionnent en plus des différents formats de nombres. Les sorties des additionneurs sont la somme et le report.2. Quelles sont les limitations de Half Adder ? Le bit de retenue généré à partir du bit précédent ne peut pas être ajouté est la limitation de cet additionneur. Pour effectuer l'addition de plusieurs bits, ces circuits ne peuvent pas être préférés.3. Comment implémenter un demi-additionneur à l'aide de la porte NOR ? L'implémentation de ce type d'additionneur peut également être effectuée à l'aide de la porte NOR. Ceci est une autre Porte Universelle.

K-Map for Sum (XOR) L'équation déterminée estS= A⊕ BApplicationsLes applications de cet additionneur de base sont les suivantesPour effectuer des additions sur des bits binaires, l'unité arithmétique et logique présente dans l'ordinateur préfère ce circuit additionneur. à la formation du circuit Full Adder. Ces circuits logiques sont préférés dans la conception des calculatrices. Pour calculer les adresses et les tables, ces circuits sont préférés. Au lieu d'une simple addition, ces circuits sont capables de gérer diverses applications dans les circuits numériques. De plus, cela devient le cœur de l'électronique numérique.Code VHDLLe code VHDL pour le circuit Half Adder islibrary ieee;utiliser ieee.std_logic_1164.all;entity half_adder isport(a,b: in bit; sum, carry:out bit);end half_adder ;données d'architecture de half_adder isbeginsum<= a xor b;carry <= a et b;end data;FAQs1. Qu'entendez-vous par Adder ? Les circuits numériques dont le seul but est d'effectuer l'addition sont appelés Adders. Ce sont les principaux composants des ALU. Les additionneurs fonctionnent en plus des différents formats de nombres. Les sorties des additionneurs sont la somme et le report.2. Quelles sont les limitations de Half Adder ? Le bit de retenue généré à partir du bit précédent ne peut pas être ajouté est la limitation de cet additionneur. Pour effectuer l'addition de plusieurs bits, ces circuits ne peuvent pas être préférés.3. Comment implémenter un demi-additionneur à l'aide de la porte NOR ? L'implémentation de ce type d'additionneur peut également être effectuée à l'aide de la porte NOR. Ceci est une autre Porte Universelle. Demi-additionneur utilisant des portes NOR4. Comment implémenter Half Adder à l'aide de la porte NAND ? La porte NAND est l'un des types de portes universelles. Cela indique que tout type de conception de circuit est possible grâce à l'utilisation de portes NAND.

Demi-additionneur utilisant des portes NOR4. Comment implémenter Half Adder à l'aide de la porte NAND ? La porte NAND est l'un des types de portes universelles. Cela indique que tout type de conception de circuit est possible grâce à l'utilisation de portes NAND. Demi-additionneur À partir du circuit ci-dessus, la sortie de report peut être générée en appliquant la sortie d'une porte NAND à l'entrée en tant qu'autre porte NAND. Ce n'est rien d'autre que familier à la sortie obtenue à partir de la porte ET. L'équation de sortie de SUM peut être générée en appliquant la sortie de la porte NAND initiale avec les entrées individuelles de A et B à d'autres portes NAND. Enfin, les sorties obtenues par ces portes NAND sont à nouveau appliquées à la porte. Par conséquent, la sortie pour la SOMME est générée. Par conséquent, l'additionneur de base dans le circuit numérique peut être conçu en utilisant diverses portes logiques. Mais l'addition de plusieurs bits devient compliquée et considérée comme la limitation du demi-additionneur. Pouvez-vous décrire quel IC est utilisé pour l'opération d'incrémentation dans des compteurs pratiques ?

Demi-additionneur À partir du circuit ci-dessus, la sortie de report peut être générée en appliquant la sortie d'une porte NAND à l'entrée en tant qu'autre porte NAND. Ce n'est rien d'autre que familier à la sortie obtenue à partir de la porte ET. L'équation de sortie de SUM peut être générée en appliquant la sortie de la porte NAND initiale avec les entrées individuelles de A et B à d'autres portes NAND. Enfin, les sorties obtenues par ces portes NAND sont à nouveau appliquées à la porte. Par conséquent, la sortie pour la SOMME est générée. Par conséquent, l'additionneur de base dans le circuit numérique peut être conçu en utilisant diverses portes logiques. Mais l'addition de plusieurs bits devient compliquée et considérée comme la limitation du demi-additionneur. Pouvez-vous décrire quel IC est utilisé pour l'opération d'incrémentation dans des compteurs pratiques ?

Laisser un message

Liste des messages

Commentaires Chargement ...